#### ST. ANNE'S COLLEGE OF ENGINEERING AND

OLOGY

Approved by AICTE, New Delhi. Affiliated to Anna University, Chennai Accredited by NAAC ANGUCHETTYPALA YAM, PANRUTI - 607 106.

#### **QUESTION BANK**

**BATCH**: 2020 **PERIOD:** Jan 2024 – May 2024

2024

**BRANCH:** ECE YEAR/SEM:

III/VI

**SUBJECT:** ET3491-Embedded System and IOT

#### UNIT-I (8051 MICROCONTROLLER)

#### 1. What is mean by microcontroller?[APR/MAY 2011]

Microcontroller is a device that includes microprocessor, memory and I/O port lines on a single chip, fabricated using VLSI technology.

#### 2. What is Microcontroller and Microcomputer?[APRIL/MAY/2011]

Microcontroller is a device that includes microprocessor, memory and I/O signal lines on a single chip. Microcomputer is a computer that is designed using microprocessor as its CPU. It includes microprocessor, memory and I/O.

#### 3. Compare Microprocessor and Microcontroller. [May 2009, NOV 2006, NOV 2011] What are the differences between a microprocessor and a microcontroller? (May 2007, Nov 2011,2018)

| Sl.No | Microprocessor                            | Microcontroller                             |

|-------|-------------------------------------------|---------------------------------------------|

| 1.    | A microprocessor is a general purpose     | A microcontroller is a dedicated chip       |

|       | device which is called a CPU.             | which is also called single chip computer.  |

| 2.    | A microprocessor does not contain on chip | A microcontroller includes RAM, ROM,        |

|       | I/O Ports, Timers, Memories etc.          | serial and parallel interface, timers,      |

|       |                                           | interrupt circuitry in a single chip.       |

| 3.    | Microprocessor is used as the CPU in      | Microcontroller is used to perform control- |

|       | microcomputer system.                     | oriented applications.                      |

| 4.    | Microprocessor instructions are nibble or | Microcontroller instructions are both bit   |

|       | byte addressable                          | addressable as well as byte addressable.    |

#### 4. List the features of 8051 microcontroller. [MAY 2007] [NOV 2007, NOV 2011]

The 8051 is an 8-bit Microcontroller:

- ✓ The CPU can work on only 8 bits of data at a time

- ✓ The 8051 has

- 128 bytes of RAM

- 4K bytes of on-chip ROM

- Two timers

#### 5. List the applications of microcontroller. [MAY/JUNE 2009]

Microcontroller is used various control applications:

- Fire detection in Building.

- Industrial control(process control)

- Motor speed control (stepper motor control)

- Peripheral devices(printer)

- Stand alone devices(color Xerox machine)

- Automobile applications(power steering)

- Home applications (washing machine, AC)

#### 6. Mention the different operand types used in 8051. (NOV 2012)

Register operand, immediate operand, Direct operand, Direct – offset operand and Indirect operand.

- 7. What are the addressing modes supported by 8051? [May 2010, May 2009, MAY 2008, NOV2011] What are the different ways of operand addressing in 8051? (May 2016, NOV/Dec 2018)

- 1. Immediate addressing mode

- 2. Direct Addressing mode

- 3. Register addressing mode

- 4. Register indirect addressing mode

- 5. Indexed addressing mode

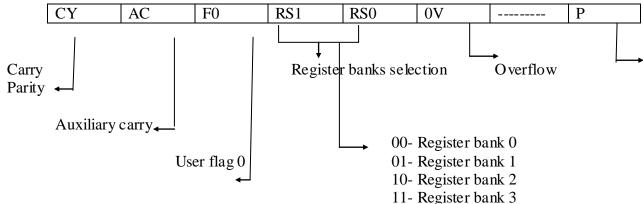

#### 8. Draw the format of PSW of 8051.(May 2015)

9. State the function of RS1 and RS0 bits in the flag register of Intel 8051 microcontroller.[NOV2011]

How do you select the register bank in 8051 micro-controller? (May 2010, NOV 2008, May 2008, May 2016)

Mention the number of register banks and their addresses in 8051. (NOV 2015)

✓ RS1 & RS0 are used to indicate which bank currently in use.

| RS1 | RS0 | Register bank   | Addresses of   |

|-----|-----|-----------------|----------------|

| K31 | K30 | Selection       | Register banks |

| 0   | 0   | Register Bank 0 | 00H to 07H     |

| 0   | 1   | Register Bank 1 | 08H to 0FH     |

| 1   | 0   | Register Bank 2 | 10H to 17H     |

| 1   | 1   | Register Bank 3 | 18H to 1FH     |

RS1, RS0 – Register bank select bits

10. In the program status word of 8051, the bits RS0 and RS1 are 1 and 0, then which register bank is selected for operation? (AU May 2013)

Register Bank 1 is selected.

11. Explain the 16-bit registers DPTR of 8051.[MAY/JUNE 2007] What is the use of DPTR? (May2009)

DPTR: DPTR stands for data pointer. DPTR consists of a high byte (DPH) and a low byte (DPL). Its function is to hold a 16-bit address.

It may be manipulated as a 16-bit data register or as two independent 8-bit registers. It serves as a base register in external data transfer.

#### 12. What are the advantages of microcontroller over microprocessor?

### What are the advantages of using a microcontroller in place of a microprocessor? (AU May 2011 MAY 2008)

- The overall system cost is low, as the peripherals are integrated in a single chip.

- The size is very small.

- The system is easy to trouble shoot and maintain.

- The system is more reliable.

#### 13. Define XTAL1 and XTAL2. [MAY/JUNE 2009]

- These two pins are connected to Quartz crystal oscillator which runs the on-chip oscillator.

- If use a source other than the crystal oscillator, it will be connected to XTAL1 and XTAL2 is left unconnected.

### 14. Name the special functions registers available in 8051.[MAY2007, NOV 2007, May 2008, May 2010]

- Accumulator

- B Register

- Program Status Word

- Stack Pointer

- Data Pointer

- Port 0, Port 1, Port 2 & Port 3

- Interrupt priority control register

- Interrupt enable control register

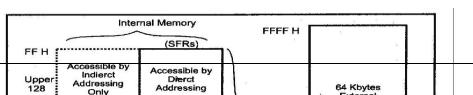

### 15. What is the importance of special functions registers available in 8051 microcontroller?

- ✓ The 8051 operations that do not use the internal 128 byte RAM address from 00H to 7FH.

- ✓ 128 byte RAM locations used by a group of special internal registers.

- ✓ SRFs (special function registers), which may be addressed like internal RAM.

### 16. How is stack implemented in 8051? (or) What is stack pointer and write the stack level of 8051? (NOV 2007)

- ✓ The 8051 LIFO: Stack can reside anywhere in the internal RAM.

- ✓ It has 8 bit stack pointer to indicate the stop of the stack using PUSH and POP instructions.

- ✓ During PUSH the SP is incriminated by one and POP the SP is decremented by one.

#### 17. What is the use of RET and RETI instruction in 8051?

RET – Return to subroutine

Used to return from a subroutine previously entered by CALL instructions

RET – Return to interrupt

Used at the end of interrupt service routine(ISR)

#### 18. List the 8051 instructions that affect the flags. [NOV/DEC 2007]

ADD, ADDC, DIV, MUL and SUB B

#### 19. List the 8051 instructions that always clear the carry flag.

CLR C, DIV, MUL

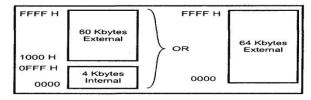

#### 20. Give the functions of the EA pin of 8051. (NOV 2016)

### How the processor 8051 does know whether on-chip ROM or external program memory is used? (May 2014)

EA: EA stands for External Access.

- ✓ This pin is an active low pin. This pin should not be left unconnected.

- ✓ This pin is connected to ground when microcontroller is accessing the program code stored in the external memory.

- ✓ This pin is connected to Vcc when it is accessing the program code in the on chip memory.

#### 21. Give the function of the SP register of 8051. [ NOV/DEC2011]

SP: SP stands for stack pointer.

- ✓ SP is an 8-bit wide register.

- ✓ It is incremented before data is stored during PUSH and CALL instructions.

- ✓ The stack pointer is initialized to 07H after a reset.

### 22. What are the functions of the following signals of 8051? ALE/PROG, PSEN. (AU Nov 2010)

#### **ALE (Address Latch Enable):**

- ✓ This is an output pin and is active high.

- ✓ When connecting an 8051 to external memory, Port 0 provides both address and data.

- ✓ If ALE=0, Port 0 ( $D_0$ - $D_7$ ). If ALE=1,it has ( $A_0$ - $A_7$ ).

#### **PSEN** (Program Store Enable):

- ✓ This is an output pin.

- ✓ In 8051-based system in which an external ROM holds the program code, this pin is connected to the OE pin of the ROM.

#### 23. Give the alternate functions for the port pins of port 3. [APRIL/MAY 2011]

#### Which port used as multifunction port? List the signals. (April 2017)

#### Port 3 is used as multifunction port and its signals are

- ✓ RD Read data control output

- ✓ WR Write data control output

- ✓ T1 Timer / Counter1 external input or test pin

- ✓ T0 Timer / Counter0 external input or test pin

- ✓ INT1 Interrupt 1 input pin

- ✓ INTO Interrupt 0 input pin

- ✓ TXD Transmit data pin for serial port in UART mode

- ✓ RXD Receive data pin for serial port in UART mode

#### 24. List the ports available in 8051. (or)

#### How many ports are bit addressable in 8051? (NOV 2011, NOV 2009)

- ✓ The four ports are P0 (Port 0), P1 (Port1), P2 (Port 2) and P3 (Port3).

- ✓ Four ports are bit addressable.

## 25. How does the status of EA pin affect the access to internal and external program memory?

- ✓ If EA=0, 8051 can access the external program memory.

- ✓ EA=1, accesses the internal program memory.

### 26. What is the size of the on-chip program memory and on-chip data memory of 8051 microcontroller? (AU May 2012, NOV 2011)

✓ The size of the on-chip program memory of 8051 microcontroller :4K

✓ The size of the on-chip data memory of 8051 microcontroller :128 bytes

#### 27. What is the difference between timer and counter operations in 8051?

- ✓ The timer, counts the internal clock pulses whose frequency is 1/12<sup>th</sup> of oscillator frequency.

- ✓ The counter, counts the external clock pulses which are given through T0 pin and T1 pin of 8051.

#### 28. Define watch dog timer.

- ✓ Watch dog timer is a dedicated timer to take care of system malfunction.

- ✓ It can be used to reset the controller during software malfunction.

#### 29. What is the function of TMOD register?

- ✓ TMOD (timer mode) register is used to set the various timer operation modes.

- ✓ TMOD is dedicated to the two timers (Timer 0 and Timer 1).

# 30. If a 12 MHz crystal is connected with 8051, how much is the time taken for the count in timer 0 to get incremented by one?

Baud rate =

$$\frac{\text{oscillator frequency}}{12}$$

=  $\frac{12\text{MHz}}{12}$  =  $1\text{MHz}$

T=1/f=1/1MHz=1 micro sec

### 31. What is the time duration for one state and one machine cycle if a 6MHz crystal is connected to 8051?

Clock frequency=6MHz/12=0.5MHz

One T state = 1/clock frequency = 1/0.5 MHz = 2 micro sec

The time taken to execute a machine cycle is 12 clock periods.

#### 32. What happens in power down mode of 8051 micro controller? (May 2016)

- ✓ The memory locations of power down RAM can be maintained through a separate small battery backup supply.

- ✓ So that the content of these RAM can be preserved during power failure conditions.

#### 33. Define baud rate. (May 2016)

- ✓ Baud rate is used to indicate the rate at which data is being transferred.

- ✓ Baud rate = 1/Time for a bit cell

#### 34. Give the register IE format of 8051. (or)

Mention the use of interrupt enable register in 8051. (May 2009)

- ✓ EA Enable all control bit

- ✓ ET2 Timer w interrupt enable bit

- ✓ ES Enable serial port control bit

- ✓ ET1 Enable Timer 1 control bit

- ✓ EX1 Enable external interrupt 1 control bit

- ✓ ET0 Enable Timer control bit

- ✓ EX0 Enable external interrupt control bit

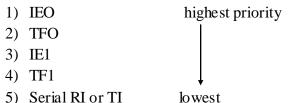

- 35. Name the interrupt sources of 8051 for which the priority levels are highest, lowest respectively.

## 36. What is the function of IP register in 8051? (or)What register keeps track of interrupt priority in the 8051? Explain. (NOV 2009)

The IP register is used to set high priority to one or more interrupts in 8051.

|  |  | PS | PT1 | PX1 | PT0 | PX0 |

|--|--|----|-----|-----|-----|-----|

|--|--|----|-----|-----|-----|-----|

- ✓ Setting a bit, makes the corresponding interrupt to have high priority.

- ✓ Clearing a bit, makes the corresponding interrupt to low priority.

- 37. Name the five interrupt sources of 8051. [May 2010, NOV 2009, MAY2007, MAY 2008]

What is the hardware and software interrupts of 8051? Mention its vector addresses. (NOV 2011)

The interrupts with vector address are:

External interrupt 0: IE0: 0003H

Timer interrupt 0: TF0: 000BH

External interrupt 1: IE0: 0013H

Timer interrupt 0: TF1: 001BH

• Serial interrupt

Receive interrupt RI: 0023HTransmit interrupt TI:0023H

38. Draw the program memory organization in 8051.

39. Draw the data memory organization in 8051.

#### 40. Define Program Counter.

- ✓ Program counter (PC) is a 16 bit register.

- ✓ It holds the 16-bit address of the instruction to be executed by the processor.

- ✓ PC is automatically incremented after every fetch of instruction byte from the memory.

#### 41. Why all pins of a port is loaded with value "FF" before using it?

- ✓ All ports of 8051 are configured by default as Output port.

- ✓ To make it configured as Input Port, all pins of a port are loaded with value "FF" i.e., 1111 1111.

#### 42. Justify why the crystal oscillator frequency in 8051 is chosen as 11.0592Mhz.

✓ Only XTAL (Crystal Oscillator) of 11.0592 MHz can provide such standard baud rates 4800, 9600, etc., after scaling down by 12, 32 at UART.

#### 42. List the modes of Timer in 8051. (NOV 2008)

The modes of timer in 8051 are chosen with M0 & M1 bits in TMOD register. The different modes of timer are as follows.

| M1 | M0 | Mode | Description of Timer mode    |

|----|----|------|------------------------------|

| 0  | 0  | 0    | 13 bit timer                 |

| 0  | 1  | 1    | 16-bit timer                 |

| 1  | 0  | 2    | 8-bit timer with auto reload |

| 1  | 1  | 3    | Split timer                  |

#### 43. What is the significance of C/T bit in TMOD register of 8051?

- ✓ The C/T bit in the TMOD register is a selector bit for the type of operation.

- ✓ HIGH in that bit indicates Counter operation and LOW in that bit indicates Timer operation.

#### 44. What is the significance of TRx bit in TCON register of 8051? (May 2015)

TRx bit in the TCON register is used to Start / Stop the timer register for both timer and counter operation, by setting that bit with value '1' / '0' respectively.

#### 45. What are the modes of asynchronous serial communication in 8051? (NOV 2008)

✓ The mode of serial communication is decided by two bits SM0 & SM1 in

SCON register.

✓ The detail of the various modes is given below.

| SM1 | SM0 | Mode | Serial Mode Description | Baud rate                   |

|-----|-----|------|-------------------------|-----------------------------|

| 0   | 0   | 0    | 8-bit Shift register    | F <sub>Osc</sub> / 12       |

| 0   | 1   | 1    | 8-bit UART              | Variable                    |

| 1   | 0   | 2    | 9-bit UART              | F <sub>Osc</sub> / 32 or 64 |

| 1   | 1   | 3    | 9-bit UART              | Variable                    |

#### 46. Illustrate the CJNE instruction. (April 2017)

Compare and Jump if Not Equal – CJNE

Compare the magnitude of the two operands and jump if they are not equal.

The values are considered to be unsigned.

The Carry flag is set / cleared appropriately.

Example: CJNE A, direct, rel

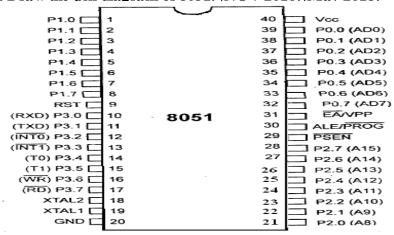

#### 47. Draw the pin diagram of 8051. (NOV 2016)(May 2018)

#### 48. What is jump range? (NOV 2015)

What is the difference between AJMP and LJMP instruction? (May 2014)

| Jump Instruction | Meaning       | Jump Range |

|------------------|---------------|------------|

| SJMP             | Short jump    | 256B       |

| AJMP             | Absolute jump | 2KB        |

| LJMP             | Long jump     | 64KB       |

- AJMP and LJMP instructions are transfer program control to the specified vector address.

- Program control transfer ranges are 2KB for AJMP and 64KB for LJMP.

### **49.** What are special function registers used for port operation in 8051? (May 2012) P0, P1, P2 and P3 SFRs used for port operation.

#### 50. What is need for bitwise instructions in microcontroller? (May 2012)

Bitwise instructions allow manipulating the individual bits of bit addressable registers and memory locations as well as the CY flag.

### 51. What are on-chip resources? List those available in the 8051 microcontroller. (NOV 2010)

When various resources available inside of chip is known as on-chip resources. On-chip resources available in 8051 are RAM, ROM, Timer, Interrupts, serial ports and parallel ports.

### 52. A given 8051 chip has a speed of 16MHz. What is the range of frequency that can be applied to the XTAL1 and XTAL2 pins? (NOV 2009)

16MHz frequency can be applied to the XTAL1 and XTAL2 pins.

### 53. How do you calculate baud rate for serial communication for 8051? (NOV 2007, MAY 2013,2015)

8051 divides the crystal frequency by 12 to get machine cycle frequency.

8051 UART circuitry divides the machine cycle frequency by 32.

Timer 1 is used to set baud rate using TH1 register

| Baud rate | TH1 (decimal) | TH1(Hex) |

|-----------|---------------|----------|

| 9600      | -3            | FD       |

| 4800      | -6            | FA       |

| 2400      | -12           | F4       |

| 1200      | -24           | E8       |

#### 54. Why it is necessary to have external pull up for port 0 in 8051? [November 2014]

- ✓ When logic -1 is loaded to the latch.

- ✓ This causes port 0 to float to high impedance state and it gets connected to the Pin read buffer.

- ✓ An external pull up resistor is required to supply a high output.

#### **PART-B**

- 1. Draw the architectural block diagram of 8051 microcontroller and explain. (NOV 2011, MAY 2010, NOV 2009, NOV2008, May 2008, MAY 2007, MAY 2006, NOV 2016, May 2016)

- 2. Give PSW of 8051 and describe the use of each bit in PSW. (NOV 2015)

- 3. Explain in detail the internal memory organization of 8051 microcontroller (NOV 2014, May 2012, NOV 2011, NOV 2010, May 2010, MAY 2009, NOV 2008, NOV 2007)

- 4. Write the available special function registers in 8051. Explain each register with its format and functions. (April 2017, NOV 2015) .(Nov/Dec 2018)

- 5. What are the I/O ports available in 8051 and explain? (MAY 2014, NOV 2012, MAY2010, NOV2009,2018)

Enumerate about the ports available in 8051. (MAY 2014)

Explain parallel port architecture of 8051 microcontroller. (NOV 2012)

Explain each PORT circuitry available in 8051. (NOV 2007)

- 6. Explain interrupt structure of 8051 microcontroller. (NOV 2011, MAY 2009)

- 7. Explain in detail the timer of 8051 and their associated registers. (NOV 2009, MA Y2009) How are the timers of 8051 used to produce time delay in timer mode? (NOV 2011)

- 8. Explain Pin details of 8051 microcontroller. (MAY 2006)

Describe the functions of the following signals in 8051. RST, EA, PSEN and ALE. (NOV 2015)

- 9. Explain different types addressing modes of 8051 microcontroller. (NOV 2008, NOV 2015, April 2017)

- 10. Discuss in detail the 8051 instruction set. (NOV 2008)

- 11. Briefly explain the data transfer instructions available in 8051 microcontroller. (NOV 2014)

- 12. With example, explain branching instructions in 8051 microcontroller. (May 2010, NOV 2012)

- 13. Explain the working of program control transfer instructions of 8051. (May 2012)

- 14. Using timers in 8051 write a program to generate square wave 100ms, 50% duty cycle. (NOV 2014, May 2016, May 2012)

- 15. Write an 8051 ALP to multiply the given number 48H and 30H. (April 2017)

- 16. Write a program to add two 16 bit numbers. The numbers are 8C8D and 8D8C. Place the sum in R7 and R6. R6 should have the lower byte. (NOV 2010)

#### 1. Whatisanembeddedsystem?(May2010)

Embedded systemisde finedas any de vice that includes a programmable computer but is not itselfintended to be a general-purpose computer. Examples: Mobile Phone, Microwave Oven

#### 2. Whataretheadvantagesanddisadvantagesofembeddedsystem?

Theadvantages of embedded systemare

• Customizationyields lower area, power and cost.

The disad vantages of embedded systemare

• Higher HW/software developmentoverheaddesign, compilers, debuggers etc., mayresultindelayedtimetomarket.

#### 3. Whataretheapplications of an embedded system?

Theembedded system is widely used in

- •Consumerelectronics, e.g., cameras, camcorders,

- •Consumerproducts, e.g., washers, micro wa veo vens,

- Automobiles (anti-lockbraking, engine control,)

- Industrial process controllers & a vionics / defense applications

- Computer/Communicationproducts, e.g., printers, FAX machines,

- Emerging multimedia applications & consumer electronics

#### 4. Differentiatetop-downandbottom-updesign.(April2014, Dec Dec21)

#### **Top-Down:**

- Topdowndesignproceedsfromtheabstractentitytogettotheconcrete design.

- Itis mostoftenusedin designingbrandnewsystems.

#### **Bottom-Up:**

- Bottom-updesignproceedsfromtheconcretedesigntogettotheabstract entity.

- It is sometimes used when one is reverse engineering a design, (i.e) when one is trying to figure out what some body else designed in an existing design.

#### 5. Whatarethetypesof real-timesystemsofanembeddedsystem?

- **Hard-real time systems:** The system where there is a high penaltyfor missingadeadline is said to be hardreal times ystem.e.g.,controls ystems for aircraft space probes/nuclear reactors; refresh rates for video, or DRAM.

- **Soft real-timesystems:** The system where there is a steadily increasing penalty if a dead line is missed is said to be soft real timesystem.

e.g., laserprinter: rated by pages-per-minute, but can take differing times to printapage (depending on the "complexity" of the page) without harming the machine or the customer.

#### 6. Whatarethevariousembeddedsystemrequirements?

$The types of \ requirements imposed by embedded applications are$

- •Functionalrequirements

- •Temporalrequirements

- •Dependabilityrequirements

#### 7. Whatarethefunctionalrequirementsofembeddedsystem?

The functional requirements of embedded systemare

- DataCollection

- Sensorrequirements

- Signalconditioning

- Alarmmonitoring

#### • DirectDigitalControl

- Actuators

- Man-MachineInteraction

- Informstheoperator of the current state of the controlled object

- Assiststheoperatorincontrollingthesystem.

#### 8. Whatare the temporal requirements of embedded system?

The temporal requirements of embedded systemare

- Tasksmayhavedeadlines

- o Minimallatencyjitter

- o Minimalerrordetectionlatency

- o Timingrequirementsduetotightsoftwarecontrolloops

- o Humaninterfacerequirements.

#### 9. Enume rate various is sue sin real time computing. (Nov/Dec 2013)

The various issues in RT computing are:

- Real-timeResponse

- Recoveringfromfailures

- Workingwithdistributedarchitecture

- Asynchronouscommunication

- Raceconditionandtiming.

#### 10. Whatarethe maincomponents of a nembed ded system? (Nov/Dec 2014)

Three main components of embedded systems are

- > TheHardware

- ➤ ApplicationSoftware

- > RTOS

### 12.Defineembeddedmicrocontroller(or)Whatistheroleofmicroprocessorin embeddedcomputing(Nov2017, Dec20, Apr21)

Anembeddedmicrocontrollerisparticularlysuited for embedded applications to perform dedicated task or operation. Example: 68 HC11 xx, 8051, PIC, 16F877, etc.

#### 13. Whata rethetypes of embedded systems?

The types of embedded systemare

- Smallscaleembeddedsystemse.g.68HC05,PIC16F8x,8051,etc.

- Mediumscaleembeddedsystemse.g.8051,80251,80x86,80196,68HC11xx

- Sophisticatedembeddedsystemse.g. ARM7, PowerPC, Intel80960, etc.

#### 14. Whatarethetwoessentialunitsofaprocessoronanembeddedsystem?

Thetwoessentialunitsof aprocessoronan embedded systemare

- Programflowcontrolunit(CU)

- Executionunit(EU)

#### 15. Summarize the challenges in embedded computing design (Dec20, Apr21 and Dec21)

- Howmuch hardware do weneed?

- Howdowemeet deadlines?

- Howdoweminimizepower consumption?

- Howdowedesignfor upgradeability?

- Does it really work?

# 16. How does the design of embedded systems differ from general purpose computing systems? (May 2023)

Embedded systems generally have a limited or no human-machine interface. For computers, the general purpose development tools can be used to develop computer software. The development of software for embedded systems requires specialized and expert tools. Computers are easily upgradable with new hardware and software.

#### 17. List the typical hardware components of an embedded platform (May 2023)

- Power supply. For the embedded system the power supply is the key component to provide the power to the embedded system circuit.

- Processor.

- Memory.

- Timers counters.

- Communication ports.

- Output and Input.

- Circuits used in application.

- Assembler.

#### 18. Enumerate the services to be provided by consumer electronics (Nov/Dec 2023)

Mobile phones, Digital camera, Robots, Point of sales terminals, Washing machine, Automatic chocolate vending machine.

## 19. What is the significance of UMI language for embedded system design? Give an example

(Nov/Dec 2023)

Unified modelling language is a visual language for specifying, controlling and documenting the artefacts of system. Example ATM, Online shopping etc.

#### 20. List the features of ARM processor.

The ARM processors provide advanced features for a variety of applications.

- Several extensions provide improved digital signal processing.

- Saturation arithmetic canbeperformed withnooverhead.

- A new instruction is used for arithmetic normalization.

- Multimedia operations are supported by single instruction multiple data operations.

- Aseparatemonitormodeallowstheprocessortoenterasecureworldto perform operations not permitted in normalmode.

#### 21. CompareCISC versus RISC (May 2023)

• Complexinstructionsetcomputers (CISC) provides a variety of instructions that may perform very complex tasks, such as string searching; they also generally used a number of different instruction formats of varying lengths.

• Reduced instruction setcomputers (RISC) tends to provide somewhat fewer and simpler instructions. The instructions were also chosen so that they could be efficiently executed in pipelined processors.

#### 22. Whatare the operating states of Cortex-M3Processor? (Dec20, Apr21)

- Thumbstate. This is normale xecution running 16-bit and 32-bit half word aligned Thumbin structions.

- DebugState. This is the statewhen the processor is in haltingdebug.

#### 23. Depict the address format for instructions in ARM processors (Dec 2022/Jan 2023)

- Register Addressing Mode

- Register Indirect Addressing Mode

- ARM's Autoindexing Pre-indexed Addressing Mode

- ARM's Autoindexing Post-indexing Addressing Mode

- Program Counter Relative (PC Relative) Addressing Mode

#### 24. How do you return from an ARM procedure? (Dec21)

On ARM, the program counter is register 15, or r15, also called pc. The instruction to call a function is bl (for immediate offsets) or blx (for addresses in registers). These instructions stores the return address in r14, called the link register, or lr. To return, we must put this value back into pc.

#### 25. Give one difference between ARM Stack and Heap (Dec2022/Jan 2023)

Stack is a linear data structure whereas Heap is a hierarchical data structure. Stack memory will never become fragmented whereas Heap memory can become fragmented as blocks of memory are first allocated and then freed. Stack accesses local variables only while Heap allows you to access variables globally.

### 26. State the advantage of inclusion of instruction and data cache in ARM Microcontroller (Dec 2022/Jan 2023)

Respectively instruction and data Cache is used to speed up processing because off-chip memory takes more processor cycles to access than does cache. But in the race for ever-faster computing, a cache isn't as simple as a memory bank for stashing data the processor might need next.

#### What is the difference between PCLK and CCLK? (

#### Nov/ Dec 2023)

PCLK is from Peripheral clock and CCLK is from CPU clock.

#### What is the concept and need for mode switching? (Nov/Dec 2023)

There are various operating modes are used in ARM processor. For example fast interrupt and Interrupt mode. To achieve efficient performance different modes and switching are supported.

#### • Whatare the components for embedded programs? (DEC20, APR21, May 2023)

Thethreestructuresorcomponentsthatarecommonlyusedinembeddedsoftware:the Statemachine, the circular buffer, and the queue.

#### 30. Definelinkers. (Dec 21)

Manyassembly languageprogramsarewrittenasse verals maller piecesrather than as single large file. Breaking a large programintos maller files helps delineate program modularity. *Linkers* allows a program to be stitched to gether out of severals maller pieces.

#### 31. Difference between Compiler and Cross Compiler (DEC20, APR21)

compiler is a software that transforms a computer program written in high-level programming language into machine language while the cross compiler is a type of a compiler that can create an executable code for a platform other than the one on which the compiler is running.

#### 32. Bring out the difference between program counter and program location counter.

(Dec 21)

Location counter is used to point available memory. Program counter is a special location counter for memory to store instruction.

### 33. State the use of breakpoints and watch points support in ARM processor. (Dec 2022/Jan 2023)

- As all the ARM processor comes with built in emulation support it supports break points as well as watch points.

- Breakpoints stops the processor wherever the location interested in and the contents of various registers can be very well examined.

- Watch points shows contents of the registers without stopping execution in between.

- Both the features are very useful in the phase of embedded hardware and software integration.

#### 34. Explain the operation of instruction (Dec 2022/Jan 2023)

ADD r3, r2, r1, LSL #3; r3:=r2+8xr1

- = r3 = r2 + r1 + 3

- = r2+8xr1=r2+r1+3

- = 8xr1-r2-r1-3

#### 35. Differentiate the role of absolute and relative addressing (May 2023)

Relative and absolute references behave differently when copied and filled to other cells. Relative references change when a formula is copied to another cell. Absolute references, on the other hand, remain constant no matter where they are copied.

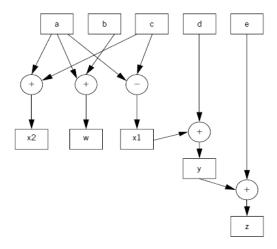

#### 36. Draw the schematic of DFG and CDFG with an example (Nov/ Dec 2023)

A DFG (Data Flow Graph) is a model of a program with no conditionals. In a high level language programming, a code segment with no conditionals. But CDFG (Control Data Flow Graph) is involved with conditinals.

\*\*\*\*

| Ques           | Question Bank: Introduction to embedded system design    |  |  |

|----------------|----------------------------------------------------------|--|--|

|                | 1. Briefly explain about the steps involved in embedded  |  |  |

| Most Important | system design.                                           |  |  |

| (90% to 100%   | 2. Enumerate the steps involved in design of model train |  |  |

| possibility)   | controller.                                              |  |  |

|                | 3. Describe the Design Methodology in detail.            |  |  |

| (40% to 50%    | 4. Enumerate the characteristics of embedded computing   |  |  |

| possibility)   | systems.                                                 |  |  |

|                | 5. Describe the Design Flows with its structure.         |  |  |

|                | 6. Explain CRC cards.                                    |  |  |

|                | Question Bank: ARM Processor and Peripherals        |  |  |

|----------------|-----------------------------------------------------|--|--|

|                | 1. Explain ARM Architecture.                        |  |  |

| Most Important | 2. Explain the features of LPC 214X Family.         |  |  |

| (90% to 100%   | 3. Discuss Instruction sets of ARM Processor.       |  |  |

| possibility)   |                                                     |  |  |

| (40% to 50%    | 4. Explain stacks and subroutines in ARM Processor. |  |  |

| possibility)   | 5. Explain the architecture of LPC214x Timer.       |  |  |

|                | 6. Explain LPC214x Pulse Width Modulation.          |  |  |

|              | Question Bank: Embedded Programming                          |  |  |  |

|--------------|--------------------------------------------------------------|--|--|--|

| Most         | 1. Briefly explain about embedded computing program          |  |  |  |

| Important    | design.                                                      |  |  |  |

| (90% to 100% | 2. Explain Program-Level Energy and Power Analysis and       |  |  |  |

| possibility) | Optimizatio n.                                               |  |  |  |

|              | 3. Explain in detail different types of testing available in |  |  |  |

|              | embedded computing.                                          |  |  |  |

|              | 4. What are the steps to be followed for optimization of     |  |  |  |

|              | execution time, power, and energy and program size?          |  |  |  |

| (40% to 50%  | 5. Write short notes on Data flow graph.                     |  |  |  |

| possibility) | 6. Write short notes on assembly and linking.                |  |  |  |

#### **UNIT 3**

#### 1. Define process. (Nov/Dec 2013)

A process is defined as a single execution of a program. A running of the same program two different times leads to creation of two different processes. Each process has its own state that includes its register and memory.

#### 2. What are the states of a process?

The states of a process are

- a. Running

- b. Ready

- c. Waiting

#### 3. What is the function in ready state?

Processes which are ready to run but are not currently using the processor are said to be in the 'ready' state.

#### 4. Define scheduling.

Scheduling is defined as the work of choosing the order of running process. It is a process of selection which says that a process has the right to use the processor at given time.

#### 5. What is scheduling policy?

Scheduling policy describes the way in which processes are chosen to get promotion from ready state to running state.

#### 6. Define hyper period.

Hyper period is the least-common multiple of the periods of all the processes. It is a finite period that covers all possible combinations of process executions.

#### 7. What is schedulability?

Schedulability indicates, any execution schedule is there for a collection of process in the system's functionality.

#### 8. What are the types of scheduling? (May/June 2013)

The types of scheduling are

- 1. Time division multiple access scheduling.

- 2. Round robin scheduling.

- 3. Cyclostatic scheduling.

#### 9. What is cyclostatic scheduling?

Cyclostatic scheduling is a type of scheduling in which schedules are separated into equal sized time slots.

#### 10. Define round robin scheduling.

Round robin scheduling is a type of scheduling which employs the hyperperiod as an interval. In this scheduling, the processes run in the given order.

#### 11. What is scheduling overhead?

Scheduling overhead is the time of execution needed to select the next execution process.

# 12. What is meant by context switching? (April 2014), (Nov/Dec 2013), (Nov/Dec 2012)(April 2018)

- A context switch is the computing process of storing and restoring of a CPU, where execution can be resumed from the same point at a later time.

- The context switching is an essential feature of multitasking operation system.

#### 13. Define priority scheduling.

Priority scheduling is defined as a scheduling which maintains a priority queue of processes that are in the runnable state.

#### 14. What is rate monotonic scheduling?

Rate monotonic scheduling is an approach that is used to assign task priority for a preemptive System.

#### 15. What is critical instant?

Critical instant is the situation in which the process or task posses' highest response time.

#### 16. What is critical instant analysis?

Critical instant analysis is used to know about the schedule of a system. It's says that, based on the periods given, the priorities to the processes has to be assigned.

#### 17. Define earliest deadline first scheduling.

Earliest deadline first scheduling is a type of scheduling which applies task priority policy that uses the nearest deadline as the criterion for assigning the task priority.

#### 18. What is use of IDC mechanism?

IDC (Inter Domain Communication) mechanism is necessary for a 'process to get communicate with other process' in order to attain a specific application in an operating system.

#### 19. What are the two types of communication?

The two types of communication are

- 1. Blocking communication

- 2. Non-blocking communication

#### 20. Give the different styles of inter process communication. (April 2014)

The different styles of inter process communication are

- 1. Shared memory communication.

- 2. Message passing.

#### 21. What is ISR? (Nov 2013)

An interrupt handler, also known as an interrupt service routine (ISR). It is a callback subroutine in an operating system. It is a device driver whose execution is triggered by the reception of an interrupt.

#### 22. List the uses of interrupts service routines?(May/June 2012)

The use of interrupts service routines are

- Input/output data transfer for peripheral devices.

- Input signals to be used for timing purpose.

- Real time executives/multitasking.

- Event driven program.

#### 23. What is meant by masking? (Nov 2013)

The priority mechanism must ensure that a lower-priority interrupt does not occur, when a higher-priority interrupt is being handled. The decision process is known as *masking*.

#### 24. Write about non-maskable interrupt.

The highest-priority interrupt is normally called as *Non-Maskable Interrupt* (*NMI*). The NMI cannot be turned off. It is usually reserved for interrupts caused by power failures. The NMI can be used to save critical state in nonvolatile memory. It turns off I/O devices to eliminate spurious device operation during power down.

# 25. What are the three conditions that must be satisfied by the re-entrant function? (May/June 2012, NOV 2017)

A function is called as re-entrant function, when the following three conditions are satisfied,

- All the arguments pass the values and some of the argument is a pointer whenever a calling function calls it.

- When an operation is not atomic, the function should not operate on any variable, which is declared but passed by reference not passed by arguments in the function.

- That function does not call any other function that is not itself re-entrant.

#### 26. Define operating system.

An operating systems is defined as a program responsible for scheduling the CPU and controlling access to devices. Operating system is interface between user of a computer and computer hardware.

#### 27. List out the common tasks of operating system.

The common tasks of operating system are

- Process management

- Memory management

- Device management

- Application management

- User interface

#### 28. What is the power optimization strategies used for processes? (May/June 2013)

The power optimization strategies used for processes are

- Predictive shutdown

- Advanced Configuration and power Interface.

#### 29. What does a scheduler do in an operating system environment? (Nov/Dec 2012)

In an operating system, the scheduling process is carried out by software called scheduler.

#### 30. List out the types of scheduler.

The types of scheduler are:

- Short term scheduler

- Mid-term scheduler

- Long term scheduler.

#### 31. What is Task?

A task is an independent process that takes control of the CPU, when scheduled at an OS. Every task has a TCB (Task Control Block).

#### 32. What is Task State?

A state of a task that changes on scheduler directions. A task at an instance can be in one of the four states such as idle, ready, blocked and running. It is controlled by the scheduler.

#### 33. Define inter process communication.

An output from one task (or process) passed to another task through the scheduler. It uses signals, exceptions, semaphores, queues, mailboxes, pipes, sockets and remote procedure call. This is known as inter process communication.

#### 34. Define Semaphore.

Semaphore is a special variable or function that is used to take note of certain actions to prevent another task or process from proceeding.

#### 35. What is shared data problem?

If a variable is used in two different processes (tasks) and another task, if it interrupts without before the operation on that is completed, then the shared data problem arises.

#### 36. What is priority inversion problem? How it can be solved?

A problem in which a low priority task does not release the process for a higher priority task. An operating system can take care of this by appropriate provisions.

This problem can be solved temporarily by boosting the low priority task to higher priority task. This is called as priority inheritance.

#### 37. Briefly discuss about Deadlock situation.

Deadlock is a situation in which the processes wait for the other resource which is occupied by another process in a loop. For example take processes P1 and P2 and resources R1 and R2 in the deadlock condition.

P1 -R1 waits for R2

P2 -R2 waits for R1 so both processes waits for the other resource to get free for their complete operation.

#### 38. What is Message Queue?

A task sending the multiple FIFO or priority message into a queue for use by another task using queue message as an input is said to be message queue.

#### 39. What is Socket?

Socket provides the logical link. It is using a protocol between the tasks in a client server or peer-to-peer environment.

#### 40. What is Remote Procedure Call?

Remote Procedure Call (RPC) is a protocol that one program can use to request a service from a program located in another computer on a network without having to understand the network's details. A procedure call is also sometimes known as a function call or a subroutine call.

#### 41. Define Thread.

Thread is a minimum unit for a scheduler to schedule the CPU and other system resources. A process may consist of multiple threads. A thread has an independent process control block like a task control block. A thread also executes codes under the control of a scheduler.

#### 42. Give the uses of Task Control Block (TCB).

Task control block is a memory block which holds information of program counter, memory map, the signal (message) dispatch table, signal mask, task ID,CPU state (registers etc.) and a kernel stack (for executing system calls, etc.).

#### 43. What are the problems that may arise while using semaphores?

The problems that may arise while using semaphores are,

- (i) Sharing of two semaphores creates a deadlock problem.

- (ii) Without a timeout an ISR worst-case latency may exceed the deadline.

- (iii) A semaphore not taken, and another task use a shared variable.

- (iv) When using multiple semaphores, if an unintended task takes the semaphore, it creates a problem.

- (v) It may introduce priority inversion problem.

#### 44. What are multi rate systems? and give two examples(April/May 2023)

Multirate embedded computing systems are very common, including automobile engines, printers and cell phones. In all these systems, certain operations must be executed periodically, and each operation is executed at its own rate. Examples are automobile engines, printers and cell phones.

#### 45. What is release time and deadline of a process?

The release time is the time at which the process becomes ready to execute. A deadline specifies when a computation must be finished. The deadline for an aperiodic process is generally measured from the release time, since that is the only reasonable time reference.

#### 46. What is the period and rate of a process?

The period of a process is the time between successive executions. The process's rate is the Inverse of its period.

#### 47. What is a task graph?

A set of processes with data dependencies is called a task graph.

#### 48. Define CPU utilization.

Utilization is the ratio of the CPU time that is being used for useful computations to the total available CPU time. This ratio ranges between 0 and 1, with 1 meaning that all of the available CPU time is being used for system purposes.

#### 49. What is the response time of a process?

The response time of a process is the time at which the process finishes its execution.

#### 50. Define preemption.

Preemption is the act of forcing a process out of execution i.e. making a context switch.

## 51. If your set of processes is un-schedulable and you need to guarantee that they complete their deadlines, give possible ways to solve this problem?

The techniques available are as follows

- a. Get a faster CPU.

- b. Redesign the processes to take less execution time

- c. Rewrite the specification to change the deadlines

#### 52. What are the benefits of multithreaded programming?

The benefits of multithreaded programming can be broken down into four major categories:

- Responsiveness

- Resource sharing

- Economy

- Utilization of multiprocessor architectures

#### 53. What is a Dispatcher?

The dispatcher is the module that gives control of the CPU to the process selected by the short-term scheduler. This function involves:

- Switching context

- Switching to user mode

- I Jumping to the proper location in the user program to restart that program.

#### 54. What is dispatch latency?

The time taken by the dispatcher to stop one process and start another running is known as dispatch latency.

#### 55. What are the various scheduling criteria for CPU scheduling?

The various scheduling criteria are

- CPU utilization

- Throughput

- I Turnaround time

- Waiting time

- Response time

#### 56. Define throughput.

Throughput in CPU scheduling is the number of processes that are completed per unit time. For long processes, this rate may be one process per hour. For short transactions, throughput might be 10 processes per second.

#### 57. What is turnaround time?

Turnaround time is the interval from the time of submission to the time of completion of a process. It is the sum of the periods spent waiting to get into memory, waiting in the ready queue, executing on the CPU, and doing I/O.

#### 58. What is mailbox?

A message or message pointer from a task that is addressed to another task is said to be mail box.

### 59. State the model of Rate Monotonic Scheduling or What is Rate Monotonic Scheduling?(NOV/DEC 2018)

The simple model of the system is as follows,

- All processes run periodically on a single CPU.

- Context switching time is ignored.

- There are no data dependencies between processes.

- I The execution time for a process is constant.

- All deadlines are at the ends of their periods.

- The highest-priority ready process is always selected for execution.

#### 60. Write about POSIX (NOV 2017)

- It is a version of UNIX

- Serves as a good model for RTOS

- It has less options

#### 61. Write advantages and limitations of priority scheduling.

Advantage: Very efficient in different situations

Limitation: Very static scheduling

# 62. What is the concept of multitasking? What does it signify?(NOV/DEC 2018)(April/May 2019)

Multitasking, in an operating system is allowing user to perform more than one computer task at a time. The OS is able to track of where you are in these tasks and go from one to other without losing information.

#### 63. What is priority inheritance and priority inversion? (April/May 2019)

In one line, *Priority Inversion* is a **problem** while *Priority Inheritance* is a **solution**. Literally, *Priority Inversion* means that priority of tasks gets inverted and *Priority Inheritance* means that priority of tasks get inherited. Both of these phenomena happen in priority scheduling.

#### 64. Mention the power saving strategy adopted for real time systems(April/May 2019)

There are so many methods available to save the power in real time systems. However the main power saving is achieved through dynamic voltage scaling.

#### 65. **Define audio player**.

Audio player are defined as any media player which can only play audio files. Players capable of video playback are included under comparison of video player software, even if they are primarily well known for audio playback.

# 66. What are the basic functions of audio players? Or List out the major components of audio player (April/May 2019) (Dec2022/Jan2023)

An MP3 player performs three basic functions such as

- 1. Audio storage

- 2. Audio decompression

- 3. User Interface

#### 67. Define video accelerator or need for video accelerator (NOV 2017)(April/May2019)

Video accelerator is a hardware circuits on a display adapter that speed up full motion video, which also frees the CPU to take care of other tasks.

#### 68. Define engine control unit.

An engine control unit is a type of electronic control unit that controls a series of accelerators on an internal combustion engine to ensure optimal engine performance.

#### 69. Give one challenge in developing of codes for MPSoCs (Dec 2022/Jan 2023)

MPSoCs present unique challenges for software development due to the change from uniprocessor to many or multiprocessors (implying parallelism) and non-uniform memory structures.

The programming model of all languages such as C, C++ etc. assumes a homogeneous implementation architecture with a uniform, shared memory space. This model is incompatible with the application-specific, heterogeneous architectures of MPSoCs. This results in a mismatch between the programmer's conceptual model and the underlying implementation.

# 70. How does the ARM SAP instruction provides atomic executions? (Dec 2022/ Jan 2023)

To support the atomic instructions added in the Armv8.1 architecture, CHI-B provides Atomic Transactions. An interconnect uses Atomic Transactions to transport an atomic operation and its operands from one device to another. Using atomics instead of exclusive access reduces the amount of time during which data is inaccessible to other agents. Atomic Transactions can execute several atomic operations and can be performed internally or externally to the processor.

# 71. What is meant by requirement analysis if doing memory scaling for a video accelerator? (Dec 2022/Jan 2023)

The arithmetic on each pixel is simple, but we have to process a lot of pixels. If MBSIZE is 16 and SEARCHSIZE is 8, and remembering that the search distance in each dimension is 8 + 1 + 8, then we must perform N ops =  $(16 \times 16) \times (17 \times 17) = 73,984$ .

#### 72. What are the scheduling status considered in a process? (April/May 2023)

The operating system considers a process to be in one of three basic **scheduling states**: **waiting**, **ready**, or **executing**. At most, there is one process executing on the CPU at any time. If there is no useful work to be done, an idling process may be used to perform null operations. Any process that could be executed is in the ready state; the operating system chooses among the ready processes to select the next executing process.

#### 73. What is the significance of shared memory multiprocessors? (Nov/Dec 2023)

A shared memory multiprocessor is an architecture consisting of a modest member of processes, all of which have direct access to all the main memory in the system.

# 74. What is dynamic priority algorithm? State its advantages and applications (Nov/Dec 2023)

The priorities of the process is changed on the fly if needed so that it meets the deadline. This kind of priority very useful in real time applications such as missile, Aircraft, Bullet train etc.

#### 75. What are sporadic and aperiodic tasks? Give examples (Nov/Dec 2023)

The real time task that reoccur at any random instant and have hard deadlines are known as sporadic real time task. Example fire handling task.

The dynamic tasks that reoccur at any random time and have soft deadlines are known as aperiodic, examples keyboard, mouse.

#### 76. Definescheduling. (DEC20, APR21)

The first job of the OS is to determine that process runs next. The work of choosing the order of running processes is known asscheduling.

#### 77. What are the performance measures of real time system? (DEC20, APR21)

The following characteristics of real time operating systems can be measured: average task switch time, average pre-emption time, average interrupt latency, semaphore shuffle time, deadlock break time, and inter-task.

#### 78. Mention the limitations of RM algorithm. (Dec 21)

Deadlines must be similar to the time periods. Deadlines are deterministic. Process running with highest priority that needs to run, will preempt all the other processes.

# 79. State the control of aborting of illegal memory accesses help in fault tolerance (Dec 2022/Jan 2023)

The control of aborting of illegal memory accesses helps in fault tolerance. Each and every redundant memory blocks protected such that there is no illegal memory access for program and data. Because keeping the redundant blocks secured is very essential in achieving fault tolerance. More over the memory is very important unit next to processor in an embedded systems for overall performance.

# 80. What are the essential factors to be considered in estimating program run times? (April/May 2023)

- 1) Algorithm time complexity.

- 2) Input size.

- 3) CPU speed.

- 4) I/O waiting time.

- 5) Amount of running processes.

- 6) Amount of available memory.

- 7) Programming language used.

#### 81.Mention the method of dealing with sporadic tasks (April/May 2023)

The real-time tasks that reoccur at any random instant and have hard deadline are known as sporadic real-time tasks. Basically all the high critical tasks are sporadic tasks. For example, fire handling task in industry or emergency message arrival in system are sporadic real-time tasks. It goes through acceptance test, executed only when sufficient slack time is available and includes commands given by the system.

|              | Question Bank: Real time systems                 |  |

|--------------|--------------------------------------------------|--|

| Most         | 1. Structure of a Real Time System.              |  |

| Important    | 2. Explain the basic model of real time systems. |  |

| (90% to 100% | 3. Explain Fault Tolerance Techniques.           |  |

| possibility) |                                                  |  |

| (40% to 50%  | 4. Explain Clock Synchronization.                |  |

| possibility) | 5. Discuss about estimating program run times    |  |

|              | 6. Explain Task Assignment and Scheduling        |  |

| Question Bank: Process and operating systems |                                                           |

|----------------------------------------------|-----------------------------------------------------------|

| Most                                         | 1. Explain in detail about Inter-process communication    |

| Important                                    | mechanisms.                                               |

| (90% to 100%                                 | 2. Discuss in detail about Preemptive real time operating |

| possibility)                                 | systems.                                                  |

|                                              | 3. Design of a video accelerator                          |

|                                              | 4. Briefly discuss about various power optimization       |

|                                              | strategies for processes.                                 |

| (40% to 50%                                  | 5. Design of an Audio Player.                             |

| possibility)                                 | 6. Explain in detail the design of engine control unit.   |